에이식

에이식(ASIC; Application Specific Integrated Circuit)이란 특정한 목적에 적합하게 설계된 주문형 반도체를 말한다. 에이식이 올바른 발음이지만, 아식이라고 읽는 사람도 있다.

목차

개요[편집]

에이식은 일반적인 목적이 아니라 특정한 목적으로 사용하기 위해 필요한 스펙, 기능을 최적화시키고, 커스터마이징 하여 생산한 주문형 반도체 칩을 의미하며, 이것으로 채굴기를 만들게 되면 에이식 채굴기가 된다. 이때 이 칩을 암호화폐와 관련하여 이용한다면, 특정한 목적이라는 것은 암호화폐 채굴이라고 할 수 있는데, 보통 특정 계열의 해시 함수의 연산에 특화되어 같거나 더 적은 전력을 소모함에도 훨씬 더 많은 해시파워를 낼 수 있음으로, 그 연산 효율성이 높다. 에이식 채굴기를 이용하여 채굴하게 되면, 빠른 연산이 가능하여 블록을 생성할 확률이 높아져 채산성이 높아지며, 이익이 더 많이 생기게 된다. 이러한 에이식 채굴기는 주로 전문 채굴 업체들뿐만 아니라 일반 채굴자들도 얼마든지 구매하고 사용할 수 있다. 하지만, 개인 채굴업자들의 경우는 가동할 수 있고, 관리할 수 있는 에이식 채굴기의 수에 어느 정도 한계가 존재하고, 전기 요금에 따라 채산성이 달라질 수 있음으로, 에이식 채굴기를 이용하여 채굴한다고 하더라도 전문 채굴업자들보다 불리하다.[1]

등장배경[편집]

하이퍼캐시(HyperCash)만이 에이식 채굴로 인해 커뮤니티 및 네트워크 안정성에 발생할 수 있는 위험을 인식했던 유일한 프로젝트는 아니다. 여러 프로젝트가 에이식 저항 채굴기를 개발하고 있으며, 모네로(Monero)가 그 예이다. 비트메인(BitMain)이 모네로 및 기타 크립토나이트(CryptoNight) 알고리즘 토큰들을 채굴 할 수 있는 에이식 채굴기를 출시했을 때, 모네로 커뮤니티는 이러한 채굴기의 컴퓨팅 성능이 현재 사용 중인 다른 채굴기보다 훨씬 높을 것이라는 사실(독점 가능성)에 큰 우려가 있었다. 이를 극복하기 위해 모네로 커뮤니티는 하드포크를 통해, 에이식 저항 채굴 알고리즘을 포함하기로 했다. 하드포크의 결과는 모네로 채굴자들과 커뮤니티 구성원들에게 환영받았다. 포크 이후 모네로 토큰의 가격은 급격히 상승하였으며, GPU 채굴이 여전히 수익성이 있는 암호화폐로 알려지게 됐다. 이는 암화화폐를 소수가 아닌 모두를 위한 것이며, 익명의 어떤 회사가 수익을 얻기 위한 또 다른 수단이 아닌 것으로 바라보는 사람들에게 여전히 중요한 것이었다. 이와 같은 상태를 유지하기 위한 추가적인 노력이 모네로의 팀에 의해 구현되었다. 모네로 팀은 소셜 미디어 채널을 통해, 채굴 알고리즘을 6개월마다 바꿔서 새로운 에이식 채굴기가 개발되지 않도록 하여 궁극적으로는 네트워크를 위협하는 것을 막을 것이라고 발표했다.

또 다른 예는 지캐시(Zcash)이다. 에이식 채굴 시스템에 저항이 있는 암호화폐인 지캐시는 에이식 저항을 유지하는 방법에 대한 과학적 조언을 제공하는 기술 자문위원회를 구성했다. 마지막으로는 이더리움(Ethereum)이 있다. 2019년 초 이더리움(ETH) 핵심 개발자는 에이식 기반 네트워크 채굴 대신에 GPU 기반 효율성을 향상하는 새로운 지분증명(PoW) 알고리즘을 구현하기 위한 예비적 합의를 도출했다. 이는 에이식 채굴을 더 어렵게 만들 뿐만 아니라 네트워크 해시값을 안정화할 것이다. 많은 블록체인 프로젝트들이 에이식 채굴 저항을 이루고자 하는 것을 이해하려면 에이식 채굴기가 무엇인지 정확히 이해해야 한다. 사토시 나카모토(Satoshi Nakamoto)가 비트코인을 처음 개발했을 때, 그는 가정용 컴퓨터를 사용하여 토큰을 채굴할 수 있기를 희망했다. 특히, 그는 사람들이 트랜잭션을 검증하기 위해 CPU에 의존할 것이라고 믿었다. 그러나 비트코인 및 기타 암호화폐의 가치가 높아짐에 따라 채굴은 그 자체로 산업이 되었으며, 경쟁이 심해지고 채굴 난이도가 높아졌고, 따라서 채굴자(miner)들은 더 고급 하드웨어를 구매하고 사용하기 시작했으며, 채굴 기업들은 채굴에 최적화된 하드웨어와 알고리즘을 개발하게 되어, 결국 오늘날 에이식 채굴자가 만연하게 되었다. 그 이유는 CPU가 범용 프로세서 역할을 하기 때문이다. 즉, 다양한 기능을 처리할 수 있지만, 특정한 개별 작업을 수행하는 데는 효과적이지 않다는 것이다. 이는 그래픽 컴퓨팅을 통해 확인할 수 있는데, CPU는 그래픽 처리 및 3D 컴퓨팅 측면에서 볼 때, GPU보다 적합하지 않음으로, GPU가 만들어져 활용되고 있다.

블록체인 분야에서도 이와 같은 현상을 에이식 채굴자를 통해 확인할 수 있다. 비트코인을 채굴하기 위해서는 SHA-256 해시값을 계산해야 한다. 범용 CPU 또한 이 값을 계산할 수 있지만, 비용 및 효율성을 고려할 때 그다지 효과적이지 않다. 따라서 채굴 업체는 주 용도가 SHA-256 혹은 토큰에 따라 다른 알고리즘의 계산인 애플리케이션을 설계했다. 특정 알고리즘을 처리하도록 설계되었기 때문에 에이식의 디자인은 CPU보다 훨씬 간단하고 저렴하다. 또한 가장 중요한 것은 에이식이 채굴 관련 컴퓨팅 성능 측면에서 현재 사용되는 CPU나 GPU보다 일반적으로 수만 배 이상 높다는 점이다. 따라서 일반 CPU로는 채굴이 어려우며, 이는 시장으로 하여금 단일 목적으로 설계되고 적은 양의 파워로 운용되는 특수 하드웨어(에이식)에 투자하고 많은 자원을 사용하게 된다. 이는 결국 채굴 참가자들의 풀을 전문 채굴업자들로 제한하게 되는 효과를 낳는다. 이러한 현상은 채굴 독재자의 출현으로 이어져, 채굴자가 되기 위한 진입 장벽을 높여서 일반 사용자의 참가를 차단하게 된다.[2]

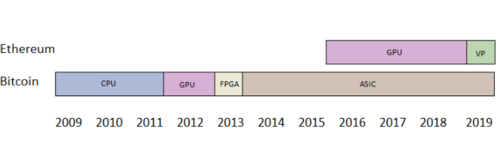

- 채굴칩 에이식까지의 변화 과정

비트코인이 출시된 2009년에는 CPU 방식의 채굴이 이루어졌다. 그러나 GPU와 FPGA 설계자들은 반복되는 해시 작업에 더 최적화된 채굴 칩을 만들어냈다. 그 결과 비트코인 네트워크는 GPU 방식의 채굴로, 그 후엔 FGPA 방식의 채굴로 큰 변화의 시기를 겪었으며, 2013년에는 특정 해시 함수를 위한 설계된 에이식이 이 대열에 합류했다. CPU, GPU 그리고 FPGA와 비교해 에이식은 특정 알고리즘 실행에 훨씬 더 효율적이다. 다음은 채굴 칩 변화 과정표로 오른쪽으로 이동하고 있다.[3]

- 채굴칩 변화과정 표

< 채굴칩 변화과정 표 > 칩 종류 중앙처리장치(CPU) 그래픽 처리장치(GPU) 벡터 프로세서(VP) 응용 주문형 집적 회로(ASIC) 예시 비트코인(BTC) 2009년 ~ 2011년 비트코인 2012년 ~ 2013년, 이더리움(ETH), 모네로(XMR) 이더리움, 2018년 ~ 개발중 비트코인, 2014 ~ 현재, 모네로 오리지널(XMO) 제조사 인텔(Intel), AMD 엔비디아(NVIDIA), AMD 비트메인(Bitmain) 비트메인, 자난윈즈(Canaan Creative), 이방궈지(Ebang), 이노실리콘(Innosilicon) 생산공장 TSMC, 삼성, 글로벌파운드리(Global Foundries), 중국 인터내셔널 반도체(SMIC) TSMC, 삼성, 글로벌파운드리, 중국 인터내셔널 반도체 TSMC TSMC, 삼성, 글로벌파운드리 주사용 목적 연산 게임 암호화폐 채굴 암호화폐 채굴 작업증명방식 알고리즘 변경에 대한 영향 영향 받음 영향 받음 잠재적 영향 영향 받지 않음

특징[편집]

범용적으로 사용할 수 있는 CPU나 GPU와 같은 반도체와 달리, 에이식 반도체는 불필요한 기능을 제거함으로써 특정 목적에 최적화된 빠른 처리 속도를 낼 수 있다. 다만, 원래 목적에 맞지 않는 다른 용도로 설계를 변경하여 사용할 수 없다. 에이식은 현장에서 프로그래밍을 직접 수정할 수 있는 반도체인 FPGA에 비해 개발 시간이 길고 오류를 수정하기 어려우며 초기 개발비가 비싼 단점이 있지만, 처리 속도가 빠르고 소비전력이 작다는 장점이 있다.

채굴은 결국 정해진 인풋 안에서 조건을 충족하는 랜덤 값을 찾는 행위이다. 그런데 일반 컴퓨터 구조에서는 램에서 CPU까지 이동하는 데 많은 시간이 소요되므로, 에이식을 만들어 데이터가 계산되기까지의 시간을 최소화 하는 것이다. 또한, 에이식이 빠른 이유는 컴퓨터가 범용이기 때문이다. 게임으로도 쓸 수 있고, 음악을 들을 때와 문서를 작성할 때도 사용할 수 있다. 하지만, 에이식은 특정 목적으로만 사용되며, 사용을 위해서는 레지스터 프로그래밍 필요하기 때문에, 그만큼 속도가 빠르다.[4]

공정[편집]

에이식의 공정(Process)은 설계에 의해 배열된 회로 소자가 실린 칩을 가지고 균일한 재질의 웨이퍼 표면에 여러 종류의 불순물을 주입시켜, 산화막을 형성시키고 부분적으로 실각시키는 등의 단위 공정을 수십 차례 거쳐서 웨이퍼(wafer)의 한쪽 표면 위에 복잡한 집적회로를 형성시키는 과정을 공정이라 한다. 에이식을 제작하는 공정기술은 특정 응용에 따른 설계의 목표치에 따라 정해지는데 현재 이용되는 기술로는 시모스(CMOS), 바이포울러(Bipolar), 바이시모스(BiCMOS), 갈륨비소(GaAs) 등이며, 각 공정 기술은 에이식 설계 방법인 완전 주문형, 반주문형, 설계 가능 논리 소자(PLD) 등에 사용된다. 시모스 기술은 낮은 소비전력, 손쉬운 설계, 높은 집적도, 지속적인 성능 개선에 힘입어 가장 많이 이용되고, 현재 에이식 설계의 가 시모스로 되어 있다. 바이시모스 기술은 바이포울러의 장점인 높은 구동력과 시모스의 장점인 높은 집적도와 낮은 소비전력을 결합시킨 것으로, 칩의 스피드/소비전력 면에서 장점을 가진다. 바이포울러는 논리소자로 고속인 이미터-결합 논리(ECL)회로를 채택하고 있는데, 높은 소비전력 때문에 10,000 게이트 이하에서 주로 쓰인다. 갈륨비소는 에이식에 극히 일부 이용되고 있지만, 초고속용에 그 쓰임새가 확대되어 나갈 전망이다.

- 후공정

후공정이란 설계가 완료된 시점에서부터 설계된 데이터를 이용하여 칩 제작, 공정, 테스트, 팩키지를 하여 최종적으로 칩을 보드나 시스템에 장착할 수 있을 때까지 일련의 순서를 총칭하는 말이다. 에이식 칩의 다양화 및 고집적을 위해 공정기술이 서브마이크론(sub micron)화 됨에 따라 후공정 전반에 대한 기술개발이 한층 더 중요시되고 있다.[5]

테스트와 패키지[편집]

- 에이식 테스트

에이식 테스트의 목적은 제조 공정상에서 발생할 수 있는 개방(Open), 단락(Short) 등의 물리적 결함이나 설계상 에러 등을 검사(Test)하는 것으로써, 철저한 검사가 이루어지지 않는 경우에는, 에이식 칩의 성능 및 안정도에 막대한 지장이 있다. 검사의 종류로는 웨이퍼 상태에서 프로빙(Probing)하는 전기다이 정렬(EDS)과 패키지 상태로 검사하는 파이널 테스트(Final Test)의 두 가지 방식이 있다. 테스팅의 형태를 크게 두 종류로 나누면 첫 번째로, 파라메틱 (Parametric) 검사로서 각 칩에 대해 입력과 출력 단자의 전압 또는 전류를 측정하는 단락 검사(Short test), 개방 검사(Open test), 최대 전류 검사(Maximum current test), 누설 검사(leakage test), 출력 구동 전류 검사(Output drive current test), 임계 레벨 검사(Threshold level test) 등의 DC 파라메틱 검사와 회로 내의 임계 경로 검사와 같이 전파 지연 검사(Propagation delay test), 셋업과 보유 시간 검사(Set and hold time test), 상승 하강 시간 검사(Rise fall time test) 등과 같은 AC 파라메틱 검사가 이에 속한다. 두 번째로, 시뮬레이션 결과를 이용한 테스트 벡터(Test vector)를 가지고, 에이식 칩의 내부 노드를 테스트하여 디자인 동작을 검사하는 기능 검사(Functional test)가 있다. 검사에 사용되는 장비로는 에이식 칩의 평가 및 검증용 테스터와 생산용 테스터 등이 있다.

- 에이식 패키지

에이식 패키지는 외부 환경으로부터 반도체 소자를 보호하고, 사용과 취급이 용이하도록 플라스틱, 세라믹 또는 금속을 이용하여 칩을 패키지하는 것으로 외부 형태 및 사용물질의 종류에 따라 다양하게 나눌 수 있다. 과거에는 소자의 기본적 기능을 만족시키는 선에서 조립되었고, 현재는 소자의 다양한 특성과 기능 및 용량을 더욱 더 효율적으로 수행할 수 있는 패키지를 만들 수 있는가에 집중되어 있다. 특히 에이식 제품과 같이 I/O 핀 수의 증가, 칩의 수축 화, 세트의 경박단소화 등에 따라 이를 조립할 패키지도 역시 많은 제약을 받게 되며, 제품의 특성을 수용할 수 있는 신규 패키지가 계속 개발되고 있다. 현재 가장 많이 이용되는 패키지 타입은 쿼드 플랫 패키지(Quad Flat Package)와 핀 그리드 어레이(Pin Grid Array) 및 테이프 캐리어 패키지(Tape Carrier Package)다. 이들 모두 칩의 고집적화에 따른 다핀화 즉 패키지의 고 밀화가 유리한 타입이지만 각기 약간의 특성이 있어 그 용도에 따라 패키지를 하게 된다. 에이식 패키지의 향후 방향은 플라스틱 수지로 칩을 감싸서 보호하던 개념에서 보드 위에 칩을 직접 붙여 칩과 보드를 전기적으로 배선 연결(Wire Bonding)하는 칩온보드(Chip On Board)와 마이크로 범프 본딩(Micro bump bonding) 방법으로 배선 없이 바로 보드 위에 칩을 붙여, 축적도를 높이고, 가격과 보드에 효율적인 이용이라는 측면에서 큰 장점이 있는 나칩(Bare chip) 기술이 향후에 크게 활용될 것이다.[5]

디자인 킷[편집]

에이식의 설계과정 중 설계용 소프트웨어(S/W)는 에이식의 생산성을 좌우하는 매우 중요한 요소 중의 하나이다. 현재 전자 설계 자동화(EDA) 시장에서는 매우 다양한 설계용 소프트웨어가 출시되어있다. 일반적으로 에이식을 필요로하는 곳은 시스템을 설계하여, 제품을 생산하는 세트 업체이며, 이들은 이러한 세트를 설계하기 위한 나름대로의 설계 환경을 구비하여 사용하고 있다. 과거 세트 업체에서 원하는 에이식을 개발하기 위해서는 에이식 회로와 입/출력값을 에이식 제작회사에 전달하여 에이식 제작 회사가 수행하는 방법을 이용하였다. 그러나 이러한 방법을 이용하면, 짧은 제품의 수명에 대처할 방법을 잃게 되어 적절한 시기에 세트업체의 제품을 출시할 기회를 놓치게 된다. 세트 업체의 설계자가 그들의 설계환경에서 직접 에이식을 설계할 수 있도록 에이식 제조회사는 적절한 설계 환경을 제공하게 되었다.

에이식 설계환경은 에이식 디자인 킷과 에이식 제조회사가 직접 사용하는 에이식 디자인 시스템 두 가지로 크게 구분된다. 에이식 디자인 시스템은 일명 골든 툴(Golden Tool)이라 하기도 하는데 골든툴은 가장 중심되는 툴이라는 의미이며, 여기에서 사용되는 시뮬레이터를 골든 시뮬레이터(Golden Simulator)라고 한다. 이는 에이식 제조 회사의 에이식 공정 정보와 가장 근접한 시뮬레이션 값을 제공하는 시뮬레이터를 의미한다. 에이식 제조회사에서 사용하는 골든툴이 아닌 다른 상용 전자 설계 자동화(EDA) 툴에 에이식 제조회사의 설계정보를 주입하여 사용하는 것을 에이식 설계 킷(ASIC Design Kit)이라고 한다. 세트 설계자가 에이식 디자인 킷을 사용할 경우, 초기 시스템 설계 시부터 에이식을 고려한 설계의 수행이 가능해져 상당한 설계 기간을 단축할 수 있다. 완성된 시스템 설계자의 에이식 회로는 에이식 제조회사로 송부되어 골든 시뮬레이터를 이용해 회로 및 기능의 최종 검증을 수행한 후 에이식을 제조하기 위한 자동 배치/배선을 수행한다.[5]

디자인킷 구성[편집]

에이식을 설계하기 위한 디자인 킷은 골든툴에 비해서 상대적으로 적은 부분의 기능만을 수행할 수 있다. 에이식 디자인 킷에는 크게 두 가지의 부분이 있으며, 이의 공급은 에이식 제조회사가 책임진다.

- 라이브러리(library) : 심볼과 시뮬레이션 모델이 포함되어야 하는데, 이는 에이식의 공정정보와 매우 밀접한 관계를 맺고 있다. 심볼은 에이식 라이브러리의 기능 단위인 셀을 상징화 한 것으로서, 회로의 입력에 사용되며, 시뮬레이션 모델은 셀의 기능을 논리, 타이밍 등의 복합적인 부분을 검증할 수 있도록 준비하여 놓은 것이다.

- 인터페이스 소프트웨어(Interface Software) : 라이브러리만 가지고는 에이식 제조회사의 요구사항을 시스템 설 계자가 직접 수행하기란 무척 어려울 것이다. 에이식 제조회사는 이의 간편화 및 자동화를 위하여 에이식 디자인 킷내부에 부속 소프트웨어 유틸리티 등을 장착한다. 보통의 설계환경은 상용 탐색적 데이터분석(EDA) 공급자가 제공하는 일반적인 경로를 따라서 설계를 수행하면 되지만, 에이식 제조회사마다 특정한 에이식 정보를 갖고 있지 못해 에이식 제조사가 공급한다. 즉, 에이식 디자인 킷은 에이식 라이브러리와 인터페이스 소프트웨어라고 정의한다.

에이식의 디자인 킷은 시스템 설계자와 에이식 제조회사와의 연결고리 역할을 수행한다. 시스템 설계자는 설계환경에서 에이식 개발을 필요로하고, 에이식 제조회사에 디자인 킷을 제공 요청한다. 제공이 불가능할 경우에는, 디자인 인터페이스로 자문 요청할 수 있고, 제공이 가능할 경우는, 디자인 킷, 디자인 킷 사용설명서, 셀 라이브러리 데이터 북이 있다. 에이식 디자인 킷은 시스템 설계자와 에이식 제 조회 사와의 연결고리 역할을 수행한다. 서로의 설계환경을 이해하고 탐색적 데이터 분석 툴간의 데이터 형식의 표준화가 이루어져야만 원활한 설계 전이가 이루어질 수 있다.[5]

종류[편집]

집적회로(IC)는 필요에 따라 쉽게 구할 수 있는 집적회로들을 지칭한다. 반면, 주문형 집적회로(Custom IC)는 특별한 사용자를 위해 개발된 집적회로로써, 개발을 의뢰한 사용자에게만 공급되기 때문에, 특정한 용도의 목적에만 사용 할 수 있는 집적회로라 하여 에이식이라고 하기도 한다. 주문형 집적회로는 다시 완전주문형 집적회로(Full-Custom IC)와 반주문형 집적회로(Semi-Custom IC)로 구분되고, 반주문형 집적회로는 게이트 어레이(Gate Array)와 스탠다드 셀(Standard Cel)l로 대표되며, 스탠다드 셀의 개념을 확장하여 셀 라이브러리(Cell Library)를 포함하는 설계 방법이 응용되고 있다. 완전주문형 집적회로와 반주문형 집적회로의 구별은 향후 서로의 장점을 딴 새로운 분야의 개발이 진행될 것이다.[5]

주문형 집적회로[편집]

주문형 집적회로(Custom IC)가 가지고 있는 장점은 높은 신뢰성과 작은 면적, 빠른 속도 그리고 적은 소비전력이다. 주문형 집적회로가 고신뢰성을 갖는 것은 인쇄 회로 기판(PCB)상에 구현된 시스템을 단일 집적회로화 함으로서, 외부적 요인에 의한 손실을 줄일 수 있고, 또한 시간의 경과에 따르는 부품손상과 같은 문제점도 해결되기 때문이다. 즉 인쇄 회로 기판상에서는 여러 집적회로로 구성되기 때문에, 그중에 어느 하나에 이상이 생길 확률이 단일 집적회로에 비해서는 훨씬 높다. 이는 곧 불안정함을 의미하며, 작은 면적이란 당연히 추측할 수 있는 문제로, 한 장의 인쇄회로기판을 1개의 집적회로로 만들 수 있다. 즉, 작은 면적과 공간을 차지함으로써 시스템의 크기를 줄일 수 있게 되고, 속도와 소비전력에서도 인쇄 회로 기판상의 집적회로들과 같은 기술 수준에서 제조되었을 경우에는, 훨씬 개선된 효과를 얻을 수 있다. 이외에도 단일 집적회로화했을 경우는, 대외적으로 비밀을 보장할 수 있다는 장점을 가진다. 외부에서 그 시스템을 모방하기 위해서는 주문형 집적회로의 기능을 파악해서 만들어야만 하기 때문이고, 경제적인 면을 고려해 볼 때, 주문형 집적회로는 개 발에 소요되는 개발비용과 제품으로 생산될 경우의 양산단가가 있게 된다. 일반적으로 양산 단가는 인쇄회로 기판상에 구현되었을 경우보다는 적게 되므로, 많은 양을 생산할 경우에는 개발비용을 상쇄하여 전체적으로 볼 때, 보다 싼값으로 시스템을 구성할 수 있다.

- 주문형 집적회로의 비교

집적회로 1종을 개발하기 위하여는 대략 13장 정도의 마스크(Mask)를 이용하는 제조공정이 필요하다. 실리콘(Silicon) 원판 위에 필요한 여러 층을 쌓아 나감으로써 집적회로의 기능을 가지며, 칩 1장은 1개 레이어(Layer)에 해당한다. 같은 기술을 사용할 경우 필요한 패턴(Pattern)을 모든 레이어 하나하나에 그려 넣어야 하지만 반주문형에서는 셀 라이브러리를 이용하여 자동으로 그려 넣을 수 있다. 반주문형의 설계는 게이트 어레이를 이용하는 방법과 스탠다드 셀을 이용하는 방법으로 구분지을 수 있는데, 이들은 사용되는 칩의 수 및 규격화하는 방식에 따라 구별된다.[5]

완전 주문형 집적회로[편집]

완전 주문형 집적회로(Full-Custom IC)는 거의 모든 작업을 사람이 직접 수행하지만, 반주문형의 경우는 컴퓨터 지원설계 소프트웨어(CAD S/W)로 쉽게 작업할 수 있도록 많은 부분을 라이브러리화해놓은 것이다. 따라서 완전주문형은 사람이 원하는 대로 설계할 수 있지만, 반주문형은 설계 절차가 단순한 만큼 그에 대한 제약이 따르게 된다. 완전주문형 집적회로는 칩 면적, 속도, 소비전력 등을 고려해 볼 때, 가장 최적의 형태로 만들 수 있다. 그러나 개발비가 매우 비싸고 개발 기간 역시 오래 걸리기 때문에 주로 대량생산에 적합하다. 완전주문형 집적회로 설계는 대부분의 경우 작은 규모의 컴퓨터 지원설계 시스템을 이용하여, 모든 과정을 사람이 직접 설계해야 한다. LSI 급 정도의 집적회로를 개발할 경우에는, 적어도 몇 달 정도의 개발 기간이 필요하다. 집적회로의 개발과정은 완전주문형과 반주문형의 차이는 트랜지스터의 구성에 있다. 반주문형에서는 일정한 기능을 갖는 셀이 라이브러리로서 미리 만들어져 그것의 전기적 특성과 실제 레이아웃이 컴퓨터에 입력되어 있다. 따라서 필요한 경우는, 그 셀들을 이용해 레이아웃을 할 수 있고, 이 때문에 많은 시간을 절약할 수 있다. 완전주문형은 이와 반대로 준비된 셀들이 없기 때문에 새로 만들어야만 하고, 이 과정에 아주 큰 노력이 필요하다. 이때 설계된 셀들은 개발 집적회로에 가장 적합한 형태가 되므로 설계자가 원하는 모든 기능이 가장 이상적으로 자유롭게 실현될 수 있다.[5]

반주문형 집적회로[편집]

반주문형 집적회로(Semi-Custom IC)가 등장하게 된 이유는 주문형 집적회로의 특징을 가지면서 완전주문형 집적회로보다는 적은 노력과 적은 비용으로 빠른 기간 내에 원하는 집적회로를 제작하기 위한 것인데, 이는 궁극적으로 컴퓨터 지원설계 시스템을 쉽게 이용하는 것이다. 이와 같은 자동화는 초고밀도 집적 회로(VLSI)의 있어 더욱 중요하다. 초고밀도 집적 회로 급 정도의 고집적 집적회로를 사람이 수작업으로 개발한다는 것은 상당한 노력이 필요하므로, 결국 컴퓨터 지원설계의 이용은 필수적이다. 반주문형은 완전 주문형 설계 방법보다 칩 면적이 늘어나게 되어 특수한 기능을 필요로 하는 부분에서는 제약을 받을 수 있으나 이런 단점은 더 좋은 소프트웨어를 개발함으로써 점진적으로 개선될 것이다.[5]

설계[편집]

에이식의 개발순서로 시스템 엔지니어는 에이식 칩으로 만들고자 하는 부분에 대한 입, 출력 사양을 결정해야 한다. 결정된 입, 출력 사양에 의해 게이트 레벨의 논리회로 설계가 이루어진다. 이미 인쇄 회로 기판(PCB)상에서 게이트 레벨로 구현된 각종 회로나 FPGA들도 에이식 칩으로 용이하게 만들 수 있다. 회로설계를 하드웨어 기술언어(HDL)로 기술하여도 무방하다. 이처럼 논리회로 설계나 HD 코딩이 끝나면, 다음으로 논리 시뮬레이션(Simulation)을 한다. 하드웨어 기술언어 코딩의 경우에는, 논리합성이라는 코딩에서 회로로 바꾸는 작업이 이루어져야 한다. 논리 시뮬레이션이 끝나면 칩을 만들기 위한 실제 단계로의 레이아웃이 이루어진다. 레이아웃이 끝나면 레이아웃이 올바른지에 대한 각종 검증{포스트 심(Post-Sim), 드림캐처토큰(DRC)}등이 이루어지며, 이것이 모두 완료되면, 반도체 공장으로 데이터를 보내서 칩을 제조한다. 제조단계에서는 칩이 제대로 만들어졌는지 집적회로 테스트를 수행하며, 양품에 대해 시스템 엔지니어는 실제의 시스템에서 옳은 기능을 하는지 확인하게 되고, 이로써 에이식 칩이 완성된다. 반도체 공장으로 데이터가 보내어져서, 샘플이 나오기까지는 대략 5주에서 6주 정도가 소요된다. 시스템 엔지니어는 사양 결정 및 논리회로 설계 또는, HDL 코딩 등에서 가장 많은 시간을 소비하게 되며, 그 이후 설계순서는 각종 컴퓨터 지원설계(CAD) 툴들이 설계 자동화 개념으로 지원하고 있어, 단계별 확인작업만 해주면 된다.[5]

전단부 설계[편집]

에이식의 전단부 설계(Front-End Design)로 에이식은 일반적으로 시스템 아이디어인 알고리즘(Algorithm)이 H/W 구현 기술인 설계(Architecture)와 반도체 제조 기술인 티콜로지(technology)를 사용해 반도체 웨이퍼(Wafer)에 구현되는 IC를 일컫는다. 에이식을 설계할 때 그 영역을 3가지로 분류해 보면 동작적(Behavioral) 영역과 구조적(Structural) 영역, 실제적(Physical) 영역으로 나누어진다. 또한 2가지로 분류해 보면 전단부(Front-End) 설계와 후단부(Back-End) 설계로 구분되는데, 전단부는 물리적 영역과 구조적 영역을 합하여 일컫는 말이고 후단부는 실제적 영역에 대응 된다. 물리적 영역에서 이루어지는 일을 보면, 상품 기획을 통한 시스템 사양이 결정되면 그 시스템에 해당하는 알고리즘이 제안되고 소프트웨어적인 검증이 이루어지게 된다. 검증이 끝나면 해당 알고리즘에 대한 하드웨어(H/W) 구현을 위한 설계 가 하드웨어 기술언어를 이용해 레지스터 전송 수준(RTL) 단계까지 이루어지게 된다. 이 영역에서 주의할 점은 시스템 레벨 검증 방법이다. 일반적으로 에이식 개발비용은 매 단계마다 10배씩 증가하는 경향이 있기 때문에, 반도체 제조 기술과 무관한 소프트웨어 모델 기법을 충분히 활용하여 시스템의 알고리즘 및 설계를 충분히 검증한다. 또한, 기능 검증이 끝나고, 해당 시스템의 에이식에 대한 구체적인 사양이 필요한데, 이 사양에는 반도체 제조 기술, 특징, 상쇄기능, 블록 다이어그램, 응용 회로도, AC 특성(최대 동작 주파수), DC 특성(파워 소비량), 패키지 형태 등이 필요하게 된다. 다음으로 구조적 영역에서 이루어지는 일을 보면, 반도체 제조 기술을 선정해야 하며, 이 제조 기술과 관계되는 것이 에이식 업체가 제공하는 라이브러리이다. 이 라이브러리에는 회로 입력용 심볼과 기능 검증용 모델로 구성된 전반부 라이브러리와 실제 레이아웃용 후반부 라이브러리로 구성된다.

또한, 그 종류로는 가장 간단한 게이트와 플립플롭 등의 기본 셀과 씨램(SRAM), 롬(ROM), 그리고 멀티플라이어(Multiplier)등으 로 구성된 컴파일된 셀, 반복 구조인 비트 스라이스(Bit slice)방식의 데이터 패스 셀 등이 있다. 필요한 제조 기술선정이 되었으면, 하드웨어 구현 방법에 의해 설계 방법 이 2가지로 나뉘는데, 하드웨어 기술언어를 이용한 하향식(Top-Down) 설계 방법의 경우 하드웨어 기술언어 코드를 로직 합성이라는 자동 논리 합성 툴을 통해 라이브러리에서 필요한 게이트를 모아 게이트 레벨의 네트리스트가 만들어지고, 상향식(Bottom-Up) 설계 방법인 경우 설계를 가지고 라이브러리에서 필요한 게이트를 이용, 설계자가 직접 회로도를 입력(Schematic Capture)하여 원하는 게이트 레벨의 회로를 만드는 것이다. 이렇게 하여 만들어진 회로의 네트리스트를 가지고 논리 검증을 하게 되는데, 그 방법에는 H/W적인 방법과 소프트웨어적인 방법이 있다. 하드웨어적인 방법은 시스템 개발 초기에 많이 이용되는 방법으로 FPGA를 이용하여 시스템 보드에 실장 하여 검증하는 방법으로 빨리 실시간(Real time)검증이 가능한 장점이 있고, 소프트웨어적인 방법은 패키지를 이용해 입력된 네트리스트에 입력 신호 (Stimulus)를 가하고 예상된 결과와 회로의 출력 결과를 기능과 지연 시간(Delay)에 중점을 두어 검증하는 방법으로, 적은 비용으로 반복 작업이 용이하게 이루어지기 때문에 널리 쓰이는 방법인데 대표적인 기술은 게이트 어레이와 스탠다드 셀이 있다. 이 방법에 쓰이는 툴로는 여러 가지 레벨(RTL, Gate, Switch)을 동시에 시뮬레이션할 수 있는 믹스드 레벨 (Mixed level) 시뮬레이터, 아날로그/디지털 회로를 동시에 시뮬레이션할 수 있는 믹스드 모드(Mixed mode) 시뮬레이터가 있다. 즉, 에이식 설계과정 중 전반부 설계에서 대부분의 시간이 소요되는데, 실제 회로를 모델링한 라이브러리를 통해 시뮬레이션하기 때문에 라이브러리에 대한 충분한 이해가 앞서야 하고 주위 온도, 사용전압, 공정변화 등이 중요한 요소(Factor)이기 때문에 주위 조건을 고려하여 충분한 논리 및 지연 시간 검증을 한다. 또한, 주의할 점으로 외부 회로와 인터페이스 되는 에이식 회로 부분의 DC 특성(전류, 전압)과 AC 특성(지연시간, 부하)을 고려하여 인풋(Input)/아웃풋(Output) 버퍼를 선택해야 한다.[5]

후단부 설계[편집]

에이식 후단부 설계(Back-End Design)이다. 에이식 전단부 설계에서는 주어진 사양에 맞는 회로를 주어진 라이브러리를 이용하여 물리적 혹은 구조적으로 설계하고 검증하는 과정이다. 이렇게 S/W적으로만 설계된 회로를 실제 칩으로 구현할 때 필요한 칩 패턴 데이터, 즉 레이아웃 데이터를 생성하고 검증하는 과정을 에이식 후단부 설계라 한다. 일반적으로 회로의 레이아웃을 생성하는 방식으로는 완전주문형 방식과 컴퓨터 지원 설계(CAD) 툴을 이용한 자동 배치 합성(AlS)방식을 들 수 있는데, 완전주문형은 설계 기간이 길고 설계 비용이 많이 들기 때문에 소량 다품종의 특징을 갖는 에이식 설계에는 적합지 않다. 컴퓨터 지원설계 툴들은 일반적으로 스탠다드 셀 방식과 게이트 어레이 방식으로 레이아웃을 이용하여 셀들의 위치를 선정하고, 이들 간의 연결을 수행함으로써, 회로의의 레이아웃을 생성한다. 이외에도 데이터 패스나 메모리 블록처럼 똑같은 구조의 셀이 반복적으로 사용될 경우에는, 이 방식에 적합하게 제작된 셀의 레이아웃을 규칙적으로 조합함으로써, 면적을 최적화하는 셀 컴파일러가 있다. 레이아웃 생성 시 중요한 목적함수(Objective Function)로 칩 면적 최소화 및 전체 배선 길이 최소화를 들 수 있으며, 여기에 수반되는 몇 가지 제약 조건으로는 타이밍 제한 조건(Timing constraint)은 연결선의 길이를 제한하여 특정 노드의 신호 지연 시간을 주어진 조건에 맞추는 것과 공정 기술에 의한 디자인 룰에 어긋나지 않도록 하는 것 외에도 전력 공급에 무리가 없도록 하는 것이다. 최적의 레이아웃을 자동으로 생성하는 일반적인 배치 및 배선 과정은 다음과 같다.

- 계층적 설정(Hierarchy) : 회로 전체를 동시에 하나의 영역에 배치 및 배선을 하는 것은 문제의 복잡도가 너무 높아 최적해를 구해 내는데 어려움이 따를 뿐 아니라 각 영역의 크기에도 제 한이 있음으로 일반적으로 계층적 접근 적용된다. 이때 스키미틱상의 계층과는 상관없이 연결도나 면적 등을 고려하여 레이아웃을 위한 계층적 재설정할 필요가 있다.

- 블록 및 패드 위치 결정 : 계층 상에서 한 부분으로 묶인 일부를 블록이라 하는데 전체 배선 길이를 최소화하도록 블록 및 패드들의 위치를 대략적으로 정한다. 즉, 연결이 많은 블록일 수 록 가까이 배치시킴으로써 전체 배선 길이를 최소화한다.

- 블록 모양 결정 : 주어진 영역 내에서 블록들을 밀집하게 배치하기 위해서는 각 블록의 모양을 잘 결정해야 한다. 즉 블록 상호 간의 모양을 잘 조화시킴으로써 낭비되는 영역을 최소화한다.

- 컨넥터 위치 결정(Connector) : 각 블록의 컨넥터에 대해 그 컨넥터와 연결되어질 다른 블록들의 컨넥터 위치를 고려하여 블록의 경계면 상에서 위치를 잘 선정함으로써 전체 배선 길이를 최소화한다. 지금까지는 하향식 설계방식으로 대략적으로 소프트 블록(Soft block)들의 플로어 플래닝(Floor planning)을 하는 과정이다.

- 블록 내부의 셀 및 배선 : 먼저 블록의 내부에 대해서 완전 주문형, 스탠다드 셀 또는 게이트 어레이 방식으로 셀들을 배치하고 배선한다. 이 과정에도 역시 블록 면적의 최소화 및 전체 배선 길이의 최소화가 목적함수이며 이외에도 앞 단계에서 주어진 블록의 모양에 잘 일치하도록 배치 및 배선을 하는 것 또한 중요하다. 이 과정이 끝나면 블록들의 레이아웃이 완성되므로 컨넥터 위치나 블록의 면적 및 모양이 정확히 결정된다.

- 블록 간의 배선 : 각 블록의 레이아웃이 완성되면 그것들의 위치도 정확히 결정된다. 이 배치 상태에서 블록들간 혹은 블록과 패드 간의 컨넥터들이 연결되면 전체 레이아웃이 완성된다.

- 위에서 기술한 과정 중 어떤 특정 블록은 셀 컴파일러에 의한 검파 일된 블록과 같이 이미 레이아웃이 완성된 상태이다. 즉, 하드 블록(Hard Block)인 경우도 있을 수 있는데, 이 경우에는 블록 조정(Block orientation) 과정이 필요하다. 한 블록이 가질 수 있는 방향의 가짓수는 0°, 90°, 180°, 및 270°로 회전시킨 4가지와 반전시킨 후의 4가지 방향이 있을 수 있다. 이 8가지 방향 중 전체 배선 길이 및 전체 칩 면적을 최소화하는 한 방향을 택하는 과정이 필요하다. 레이아웃이 완성되고 나면, 배선에 의한 저항 및 캐패시턴스값을 추출하여 회로를 재 시뮬레이션 하는 과정과 공정 기술에 의존하는 디자인 규칙 검사(Design Rule Check) 및 레이아웃과 스키메틱이 잘 일치하는가를 검증한다.[5]

에이식 저항[편집]

에이식의 독점[편집]

채굴 독점으로 인한 중앙 집중화의 위협[편집]

2018년 비트코인캐시(BCH) 하드포크(Hard Fork) 전쟁으로 인해, 비트코인 가격이 하루 밤새 6,000달러 이하로 떨어져 한 번에 거의 3,000달러로 떨어졌다. 이러한 예측 불가능한 가격 하락은 암호화폐 시장의 불안정성을 증가시켰다. 이러한 하락이 발생한 이유는 하드포크 중에 두 개의 주요 채굴 업체가 전쟁을 벌였기 때문인데, 이 전쟁 기간 동안 비트코인캐시 블록체인을 정상적으로 작동시키는데, 유지되었던 컴퓨팅 파워는 동시에 다른 목적으로도 사용되어, 체인의 보안을 일부 손상했고 트랜잭션의 유효성 검사·처리를 백로그했으며, 결과적으로는 네트워크의 안정성, 수명 및 독립성에 대한 유저들의 의구심을 사게 됐다. 이 현상에서 가장 의심스러운 일들은 소위 채굴 독재자의 행동으로 인해 일어났는데, 이들의 행동은 블록체인 유저들의 공익에 부정적인 영향을 미쳤다. 그리고 이 문제가 해결되지 않으면, 결국 블록체인은 다른 중앙 집중식 메커니즘과 다를 바 없게 된다. 블록체인은 항상 탈중앙화된 기술로 여겨져 왔다. 즉, 기존 시스템보다 더 독립적이고, 공정하며, 민주적인 기술로 알려져 왔다. 분산원장의 진보와 그 장점을 고려할 때, 이러한 블록체인 기술은 세계를 변화시킬 가능성이 크다. 그러나 컴퓨팅 파워가 독점되고 일반 유저가 참여할 수 있는 능력을 상실한다면, 결국에는 다음과 같은 질문이 제기될 수밖에 없다. 이 새로운 시스템이 이전의 중앙 집중식 시스템보다 분명히 채굴 독점은 잠재력은 전체 블록체인 산업을 잠식할 것이며, 따라서 필연적으로 블록체인 기술에 대한 근본적인 신뢰를 갉아먹을 것이다.[2]

블로체인 독점의 영향[편집]

비트코인, 이더리움 및 기타 네트워크의 독점은 중앙 집중화를 유발할 뿐만 아니라 네트워크의 안정성과 보안을 손상시킬 수 있다. 이러한 독점은 마이닝풀(mining pool)의 형태를 취하기도 하는데, 이 경우 종종 의심스러운 방법들을 통해 블록 레이트를 컴퓨팅 파워 비율보다 높게 만든다. 이때 에이식부스트(AsicBoost), 셀피시 마이닝(selfish mining), 이클립스 공격(eclipse attacks) 등의 방법을 통해, 네트워크에서 컴퓨팅 파워의 51%를 소유하지 않고서도 풀 내에서 51% 공격을 가능하게 한다. 예를 들면, 버지(XVG) 블록체인에서 채굴 독재자가 네트워크 전체 컴퓨팅 파워의 10%만을 가지고서도 51% 공격을 했던 사례를 볼 수 있다.[2]

채굴기[편집]

에이식 저항성은 모든 네트워크가 구현하도록 노력해야 하는 것이 분명해 보이지만, 이러한 저항 기술에 반대하는 의견도 있다. 어떤 이들은 에이식 장비를 과학 기술의 진보에 따른 자연스러운 과정으로 간주한다. 또는, 에이식 채굴기(mining machine)가 더 저렴한 비용으로 제공되어, 네트워크 비용을 줄이는 효과를 낼 수 있다고 말한다. 일부 공동체에서의 이와 같은 두려움은 채굴기들이 일종의 기술적 진보로부터 나오는 것이기에, 네트워크가 채굴기를 몰아낸다는 것이 네트워크 자체가 기술적 진보에서 멀어지게 된다는 생각에서 비롯된다. 이에 대해 에이식 하드웨어가 과학적, 기술적 진보의 자연스러운 단계로 간주되지 않는다는 점은 명백하다. 기술적 진보는 네트워크 레벨의 기술들이 더 효율적으로 발전하고 있음을 암시하지만, 에이식 하드웨어는 이에 속하지 않는다. 만약 에이식 하드웨어가 네트워크 레벨의 기술을 더 효율적으로 발전시킨다면, 네트워크는 전기를 덜 사용하게 되어야만 한다. 하지만 비트코인의 경우, 그렇지 않은데, 비트코인이 2009년에 처음 출시되었을 때, 나가모토는 자신의 가정용 컴퓨터를 사용하여 7,200BTC 를 채굴하면서 하루에 단지 몇 킬로와트시(kWh)의 전기만을 사용했다. 현재 전 세계적으로 수만 개의 고성능 기기(에이식 기기 포함)가 하루 1,800BTC를 채굴하면서, 수백만 킬로와트시의 전기를 소비한다. 에이식 채굴기로 인해 촉발되는 이러한 하드웨어 경쟁으로 인해, 필요로 하는 것보다 더 많은 에너지를 낭비하게 된다. 더욱이, 비트코인의 블록 레이트는 일정하기 때문에 블록체인의 네트워크 처리량은 하드웨어가 아닌 네트워크의 속도에 더 의존적이다.[2]

진입장벽[편집]

이전에는 일반 개인이 암호화폐에 대해 잘 알지 못했거나, 에이식 채굴기를 구입하지 않더라도, 가정용 컴퓨터를 통한 채굴로 블록체인 산업에 참여할 수 있었다. 그러나 현재는 채굴이 일부 제한된 소수나 회사에 의해 독점되고, 에이식 채굴기의 경우에는, 주 타겟이 거대 채굴 풀 등이다. 블록체인의 가치는 컨센서스(consensus)에서 나온 것이며, 컨센서스는 더 많은 사람들의 참여로부터 발생한다. 참여율이 높을수록 더 인기 있는 블록체인이 되며, 블록체인의 인기가 높을수록 암호화폐의 가격이 안정되고 건실해진다. 즉 더 분산화될수록 산업이 보다 공정하고 안전해진다. 고속 채굴기는 블록 속도에 영향을 주지 않음으로, 기기 소유자에게 더 많은 토큰을 가져다줄 뿐, 실질적으로 네트워크를 돕는 역할은 하지 않는다. 따라서 에이식 채굴기는 기술적인 관점에서 볼 때 네트워크의 발전을 촉진하지는 않게 된다. 오히려 일반 사용자의 참여를 방해한다. 따라서, 이와 같은 독점으로 발생하는 문제를 방지하기 위해, 많은 블록체인 프로젝트들이 작업증명(PoW) 알고리즘을 포기하고 작업증명 및 위임 지분증명(DPoS) 알고리즘인 이오스(EOS)로 전환했다. 그러나 이오스의 슈퍼 노드의 관리에 대해서도 의문이 제기되었다. 예를 들어, 많은 사람들은 일반 사용자가 슈퍼 노드와 클라우드 서버에 참여하는 것이 거의 불가능하고, 블록체인이 중앙 집중화된다면, 가장 본질적인 의미에서 블록체인으로 생각할 수 있을지에 대한 의문이 제기된다. HC팀은 옐로우페이퍼를 통해서 작업증명 알고리즘이 지난 10년 동안 가장 안전하고, 공정한 컨센서스 알고리즘으로 인정되어왔기에, 그 독점 가능성에도 불구하고 완전히 포기해서는 안 된다고 이야기 되어 왔다. 따라서 HC 팀은 타협점으로서, 메인체인으로 작업증명 + 지분증명(PoS) 하이브리드 컨센서스를 채택했다. 이 둘의 조합은 강점을 키우고 단점을 보완할 수 있는 훌륭한 합의 알고리즘으로 거듭난다. HC 팀은 에이식 저항 알고리즘을 개발하고, 구현함으로써, 채굴 독재자 및 중앙 집중 문제와 같은 위험에 대비한 솔루션을 준비했다. 결과적으로, 에이식 저항 알고리즘은 커뮤니티 참여를 높이고 네트워크 보안을 강화하는 데 필요하다. HC를 포함한 각 블록체인 프로젝트들의 에이식 저항 알고리즘의 목표는 단순히 에이식 채굴기에 대한 저항만이 아니라, 블록체인에 대한 진입 장벽을 낮추고 좀 더 공정한 분산 작업증명 생태계를 구축하는 것이다.[2]

활용[편집]

에이식 반도체는 비트코인은 물론 라이트코인, 대시 등 각각의 암호화폐 알고리즘 풀이에 최적화된 반도체 칩이다. 채굴기 제조회사들은 에이식 칩에 컨트롤러 등 각종 추가 장치를 붙여 채굴기를 만든다. 에이식을 활용한 고성능 채굴기 제품은 GPU 채굴기에 비해 수백~수만 배 빠른 속도로 암호화폐를 채굴할 수 있다.

중국의 우지한 대표가 이끄는 비트메인(Bitmain) 회사는 비트코인, 대시, 라이트코인 등 암호화폐 채굴에 최적화된 주문형 반도체(ASIC)를 이용하여 앤트마이너(Antminer)라는 채굴기를 만들었다.

비트코인[편집]

비트코인(Bitcoin)은 채굴(Mining)이라는 행위를 통해 발행되는데 현재는 에이식이라는 전용 채굴기가 대부분의 비트코인을 채굴하고 있다. 이 전용 채굴기의 등장으로 소수의 채굴자가 다량의 비트코인을 채굴할 수 있는 능력을 갖추게 되었고, 이는 비트코인의 안전성을 보장해주는 블록체인의 분산화를 위협하고 있다. 초기에는 CPU를 이용하여 비트코인을 채굴하였다. 하지만, CPU는 처리기를 2~4개 밖에 갖고 있지 않음으로 채굴의 속도가 느렸다. 채굴의 속도를 높이기 위해 곧 수백 개의 처리기를 가진 GPU를 이용하여 비트코인을 채굴하기 시작했다. 그 후 2013년에 채굴만을 위한 전용 채굴 기계 에이식이 개발되었고, 현재는 대부분의 채굴자(miner)가 에이식을 사용하여 채굴하고 있다. 다음 두 표는 2013년 에이식과 그래픽카드의 해시 속도 표이다. 해시 속도는 비트코인 네트워크의 처리능력을 측정하는 단위로 1Mhash/s는 1초에 100만 개의 계산을 할 수 있음을 의한다. 두 표를 비교해보면, 2013년 에이식과 그래픽카드의 비트코인 네트워크 처리능력에 차이가 있었음을 알 수 있다.

2013년 GPU와 에이식 해시속도 GPU Mhash/s 에이식 Mhash/s GTX 660 Ti 23 Avalon ASIC 66,300 GTX 680 15 ModMiner Quad 800 GTX 670 13 X6500 FPGA Min 400 GTX 760 9 BitForce SHA256 Single 832 GTX 770 12 Butterflylabs Mini Rig 25,200 GTX 780 20

다음 두 표는 2016년의 에이식과 GPU의 해시속도 표이다.

2016년 GPU와 에이식 해시속도 GPU Mhash/s 에이식 Mhash/s Titan X 1,980 AntMiner S7 4,730,000 GTX 980 Ti 4,500 Avalon 6 3,500,000 GTX 960 Gaming 2GOC 1,173 GTX 1080 2,048 SP20 Jackson 1,500,000 GTX 1060 1,800

2013년도에는 표 중 최대 채굴 능력을 갖춘 에이식은 표 중 최대 채굴 능력을 갖춘 GPU보다 약 2,882배 채굴능력이 뛰어났으며, 2016년도에는 표 중 최대 채굴 능력을 갖춘 에이식은 표 중 최대 채굴 능력을 갖춘 GPU보다 약 1,051배 채굴능력이 뛰어났다. 즉, 에이식과 GPU의 채굴능력 차이가 약 2배 이상 줄어든 것을 확인할 수 있다. 또한 2016년도 GPU의 채굴 능력은 2013년도 에이식의 채굴능력을 따라잡았다. 이는 에이식의 채굴능력이 뛰어나다는 것을 보여준다.[6]

- 채굴에 최적인 에이식 채굴기

에이식 채굴기는 중국의 비트코인 대부 우지한(비트메인 대표)이 개발한 채굴기로 비트코인 채굴에 적합하게 개발되었다. 비트코인은 10분마다 하나씩 생성된다. 블록이 생성될 때마다 보상이 생겨나는데, 이것이 비트코인이다. 블록 생성 때마다 생겨나는 비트코인은 2008년부터 4년 단위로 절반씩 줄어든다. 이것을 반감기라 하는데, 2012년, 2016년에 각각 반감기가 있었고, 2008년에는 50비트코인, 2012년에는 25비트코인, 2016년부터는 12.5비트코인이 각각 생겨나고 있다. 총 2100만 개 중 현재 1700만 개 정도 발행되었다. 에이식 채굴기는 전기 소모량도 막대하다. 일반 PC의 20배에 달하는 1,800W를 쓴다. 그래서 채굴공장에서도 차단기 하나당 에이식 채굴기 한 대만 연결해 써야 한다. 차단기 하나당 2,000W까지 버틸 수 있는데, 에이식 채굴기는 하나가 1800W를 소모하기 때문에 두 대만 꽂아도 과전류로 차단기가 내려가 버린다.[7] ![]() 비트코인에 대해 자세히 보기

비트코인에 대해 자세히 보기

비트메인[편집]

비트메인(Bitmain)은 2018년 7월 시판 예정인 앤트 마이너 E3(the Antminer E3)를 출시했다. 모네로 체인 분할과 가정에서 GPU 방식으로 채굴하는 사람을 포함한 이더리움 커뮤니티의 다수가 비트메인의 새 채굴기에 불만족할 가능성이 높아, 비트메인은 많은 우려를 살 것이다. 신형 채굴기의 단점은 중앙집중화(centralization) 현상을 심화시킬 수 있다는 것과 기존의 이더리움 채굴 방식인 GPU에 대한 선호로 인해 이더리움 커뮤니티 내의 일부 사용자로부터 반감을 살 가능성이 있다. 신형 채굴기의 공식 사양은 전력 소모 800W(와트), 해시래이트 180MH/s(초당 메가해시)이다. 각 사양 계산 결과는 신형 이더리움 채굴기가 다른 암호화폐와 관련된 에이식 내장 채굴기보다 효율 개선(efficiency gain) 측면에서 비효율적일 수 있음을 나타낸다. 예를 들어 모네로 에이식의 효율 개선 수치가 GPU보다 높은 인 반면, 비트코인 에이식 침의 효율 개선 수치는 FPGA보다 높은 이다. 이와 대조적으로 신형 이더리움 채굴기의 효율성은 GPU보다 높지만 개선 수치는 에 불과하다. 이는 새 이더리움 채굴기에 에이식이 내장되었기 때문이 아닌, 구형 GPU 방식 채굴기보다 나중에 출시된 신형이기 때문에 나온 결과일 수 있음을 의미한다. 다음은 대략적인 채굴기 효율 개선 수치를 나타낸 것이다.[3]

< 대략적인 채굴기 효율 개선 수치 > 채굴기 및 채굴 알고리즘 해시래이트(GH/s) 전력(W) 해시 당 에너지(J/GH) 비트코인 (SHA256) CPU 0.0005 100 200,000 고성능 GPU 0.5 300 600 FPGA 0.8 40 50 고성능 ASIC 14,000 1,340 0.096 효율 개선 수치 521x 이더리움 (Ethash) 고성능 GPU 0.032 200 6,250 앤트마이너 E3 0.18 800 4,444 효율 개선 수치 1.4x 모네로 (CryptoNight) 고성능 GPU 0.0000001 200 2,000,000,000 ASIC 0.000022 500 22,700,000 효율 개선 수치 88x

베이징대학교를 나온 펀드매니저였던 우지한은 비트코인 화이트 페이퍼를 정확히 확인하고 난 후 중국어로 최초로 번역한 사람이다. 그는 비트코인의 핵심은 빨리 문제를 푸는 것임을 깨닫고 반도체 설계자를 스카웃해 와서 비트메인이라는 회사를 차렸다. 우지한이 설립한 중국의 비트메인은 전 세계 에이식 채굴기 시장의 70~80% 정도를 점유하고 있다. 우지한이 개발한 에이식 채굴기는 일반 GPU 채굴기 보다 50배 ~ 100배 더 빠르게 퀴즈를 푼다. 이렇듯, 뛰어난 에이식 채굴기를 개발한 비트메인은 이 채굴기를 소량 주문생산을 하면서 우선 중국 위주로 보급했다. 중국에 우선적으로 보급하면서 조금씩 해외에도 공급하고, 해외에서는 선주문 후 입금까지 한 후 2.5~3달을 기다려야 제품을 받아볼 수 있다.[7] ![]() 비트메인에 대해 자세히 보기

비트메인에 대해 자세히 보기

전망[편집]

이더리움 코어 개발자들이 에이식을 거부하는 작업증명(PoW) 알고리즘인 프로그래매틱 작업증명(ProgPoW)을 적용하기로 합의했다. 에이식은 특정 용도에 최적화한 주문형 반도체이다. 암호화폐 업계에선 네트워크 관리자(채굴자)가 연산 작업을 통해 블록체인을 유지할 때 각각 합의 알고리즘에 맞춘 칩으로 활용한다. 이에 에이식 채굴기는 기존 GPU 채굴 절차보다 성능과 전력 효율 면에서 우수하다. 그러나, 채굴 과정이 특정 소수에게 집중되는 결과를 초래한다는 비판을 받는다. 암호화폐 전문 매체 코인텔레그래프에 따르면 이더리움 코어 개발자들은 프로그래매틱 작업증명이 에이식의 장점을 상쇄할지가 관건이다. 개발진 중 한 명인 그렉 콜빈(Greg Colvin)은 "이미 수개월 전 여러 번 다뤘던 주제로 다시 돌아가는 데 염증이 나고, GPU파와 에이식파 사이의 논쟁이 아니라 그저 새 알고리즘에 취약점이 없는지가 중요하다”고 말했다. 프로그래매틱 작업증명 알고리즘은 지난 2019년 1월부터 거론됐다. 당시 이더리움 코어 개발진은 2월 제삼자로부터 알고리즘 감사를 받기로 하고, 안티 에이식(ANTI ASIC) 알고리즘 도입을 연기한 바 있다. 에이식에 대한 논쟁은 이더리움만의 문제가 아니다. 2018년, 지캐시 재단 또한 공식 성명을 통해 에이식 채굴을 막는 연구와 개발을 동시에 진행하겠다고 했다. 당시 중국 거대 채굴업체 비트메인이 지캐시용 에이식 채굴기를 공개했다. 또한, 2019년 3월 9일 모네로는 네트워크 업그레이드 차원에서 진행한 하드포크(hard fork) 과정에서 에이식을 우회하는 코드를 새로 도입했다. 안티 에이식 모네로는 네트워크 탈중앙화를 적절하게 보장하기 위한 것이며, 프로젝트의 목표 중 하나가 대체 가능한 화폐(fungible currency)인 만큼 소수만 채굴에 참여하는 등의 검열(censorship)에서 벗어나는 게 중요하다. 모네로의 경우에는, 안티 에이식 하드포크로 인해 한때 네트워크를 유지하는 컴퓨터 자원의 비율 해시레이트(hashrate)가 80% 가까이 떨어지기도 했다. 작업증명의 경우 다수의 관리자가 컴퓨터 자원을 동원해 분산원장(distributed ledger)을 동기화하는 게 중요하다. 즉, 해시레이트 감소는 네트워크 보안이 취약해진다는 의미이기도 하다. 실제로 2019년 1월에, 이더리움클래식은 네트워크 근간이 흔들리는 해킹 공격을 받았다. 당시 암호화폐 침체의 여파로 채굴업체와 이더리움클래식용 에이식이 줄어들면서 소규모 채굴단지를 노린 공격자들에 블록체인이 노출됐다.[8]

각주[편집]

- ↑ erc20, 〈아식 채굴이라는 것은 무엇을 의미하나요? 답변〉, 《아하》, 2019-07-14

- ↑ 2.0 2.1 2.2 2.3 2.4 hcashofficial, 〈왜 ASIC 저항인가?〉, 《네이버 블로그》, 2019-03-01

- ↑ 3.0 3.1 GRANT KIM, 〈암호화폐 시장 판도를 바꿀 수 있는 신형 이더리움 채굴기〉, 《비트멕스》, 2018-04-24

- ↑ Wysam, 〈ASIC에 대한 정확한 설명〉, 《미디오스》, 2019-01-25

- ↑ 5.00 5.01 5.02 5.03 5.04 5.05 5.06 5.07 5.08 5.09 5.10 SUN, 〈ASIC이란...〉, 《네이버 블로그》, 2005-08-28

- ↑ ASIC 채굴 방식과 GPU 채굴방식의 채굴성능 비교 PDF - https://pdfs.semanticscholar.org/e3a2/988a9ca15ceda1f3a1879bb3058e9f744e98.pdf

- ↑ 7.0 7.1 지누아빠, 〈비트코인 광풍, 아식(ASIC) 채굴기로 나도 비트코인 채굴해 볼까?〉, 《네이버 블로그》, 2017-12-04

- ↑ 김지윤 기자, 〈[https://blockinpress.com/archives/14938 이더리움, ASIC 벗어나기 본격화…채굴 전쟁 ‘현재진행형’ Facebook]〉, 《블록체인 프레스》, 2019-03-18

참고자료[편집]

- ASIC 링크드인 - https://www.linkedin.com/company/asic/

- ASIC 채굴 방식과 GPU 채굴방식의 채굴성능 비교 PDF - https://pdfs.semanticscholar.org/e3a2/988a9ca15ceda1f3a1879bb3058e9f744e98.pdf

- Wysam, 〈ASIC에 대한 정확한 설명〉, 《미디오스》, 2019-01-25

- hcashofficial, 〈왜 ASIC 저항인가?〉, 《네이버 블로그》, 2019-03-01

- erc20, 〈아식 채굴이라는 것은 무엇을 의미하나요? 답변〉, 《아하》, 2019-07-14

같이 보기[편집]

해시넷

해시넷